| Dec 11, 2022 |

|

(Nanowerk Information) Researchers at Tohoku College, the College of Messina, and the College of California, Santa Barbara (UCSB) have developed a scaled-up model of a probabilistic laptop (p-computer) with stochastic spintronic units that’s appropriate for exhausting computational issues like combinatorial optimization and machine studying.

|

|

Moore’s regulation predicts that computer systems get sooner each two years due to the evolution of semiconductor chips. While that is what has traditionally occurred, the continued evolution is beginning to lag. The revolutions in machine studying and synthetic intelligence means a lot greater computational means is required. Quantum computing is a method of assembly these challenges, however vital hurdles to the sensible realization of scalable quantum computer systems stay.

|

|

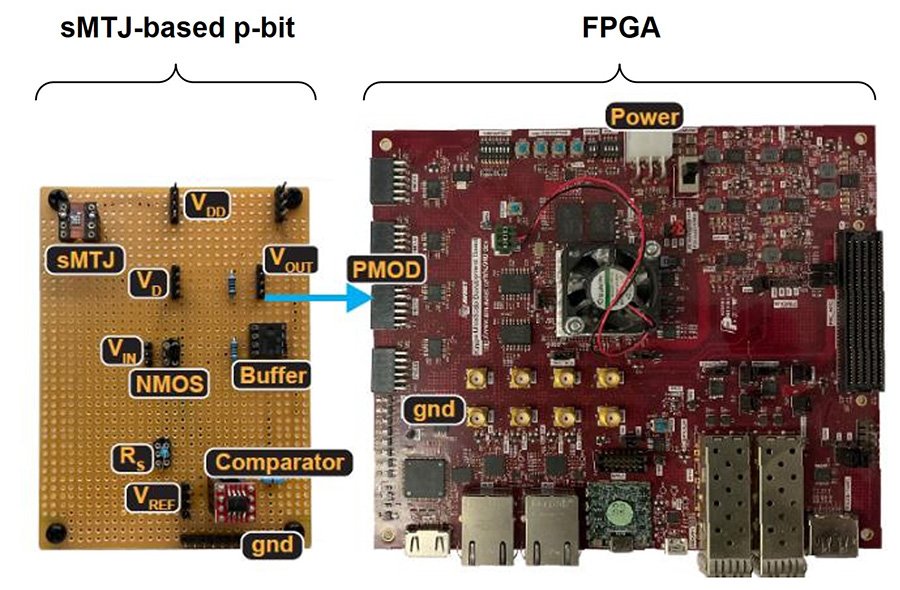

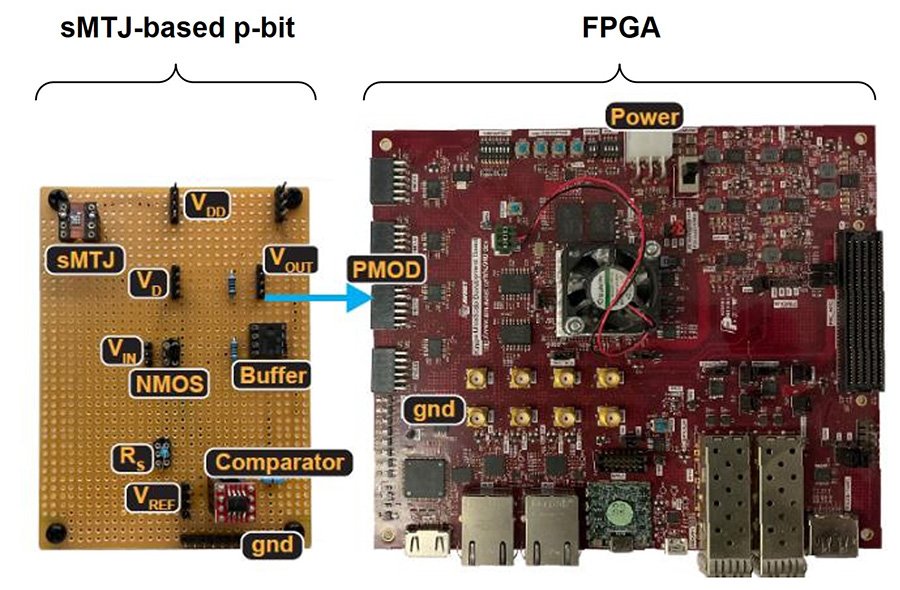

| {A photograph} of the constructed heterogeneous p-computer consisting of stochastic magnetic tunnel junction (sMTJ) based mostly probabilistic bit (p-bit) and field-programmable gate array (FPGA). (Picture: Kerem Camsari, Giovanni Finocchio, and Shunsuke Fukami et al.)

|

|

A p-computer harnesses naturally stochastic constructing blocks referred to as probabilistic bits (p-bits). In contrast to bits in conventional computer systems, p-bits oscillate between states. A p-computer can function at room-temperature and acts as a domain-specific laptop for all kinds of purposes in machine studying and synthetic intelligence. Similar to quantum computer systems attempt to resolve inherently quantum issues in quantum chemistry, p-computers try and deal with probabilistic algorithms, extensively used for classy computational issues in combinatorial optimization and sampling.

|

|

Not too long ago, researchers from Tohoku College, Purdue College, and UCSB have proven that the p-bits might be effectively realized utilizing suitably modified spintronic units referred to as stochastic magnetic tunnel junctions (sMTJ). Till now, sMTJ-based p-bits have been applied at small scale; and solely spintronic p-computer proof-of-concepts for combinatorial optimization and machine studying have been demonstrated.

|

|

The analysis group has introduced two necessary advances on the 68th Worldwide Electron Gadgets Assembly (IEDM) on December sixth, 2022 (“Experimental analysis of simulated quantum annealing with MTJ-augmented p-bits”).

|

|

First, they’ve proven how sMTJ-based p-bits might be mixed with typical and programmable semiconductor chips, particularly, Area-Programmable-Gate-Arrays (FPGAs). The “sMTJ + FPGA” mixture permits a lot bigger networks of p-bits to be applied in {hardware}, going past the sooner small-scale demonstrations.

|

|

Second, the probabilistic emulation of a quantum algorithm, simulated quantum annealing (SQA), has been carried out within the heterogeneous “sMTJ + FPGA” p-computers with systematic evaluations for exhausting combinatorial optimization issues.

|

|

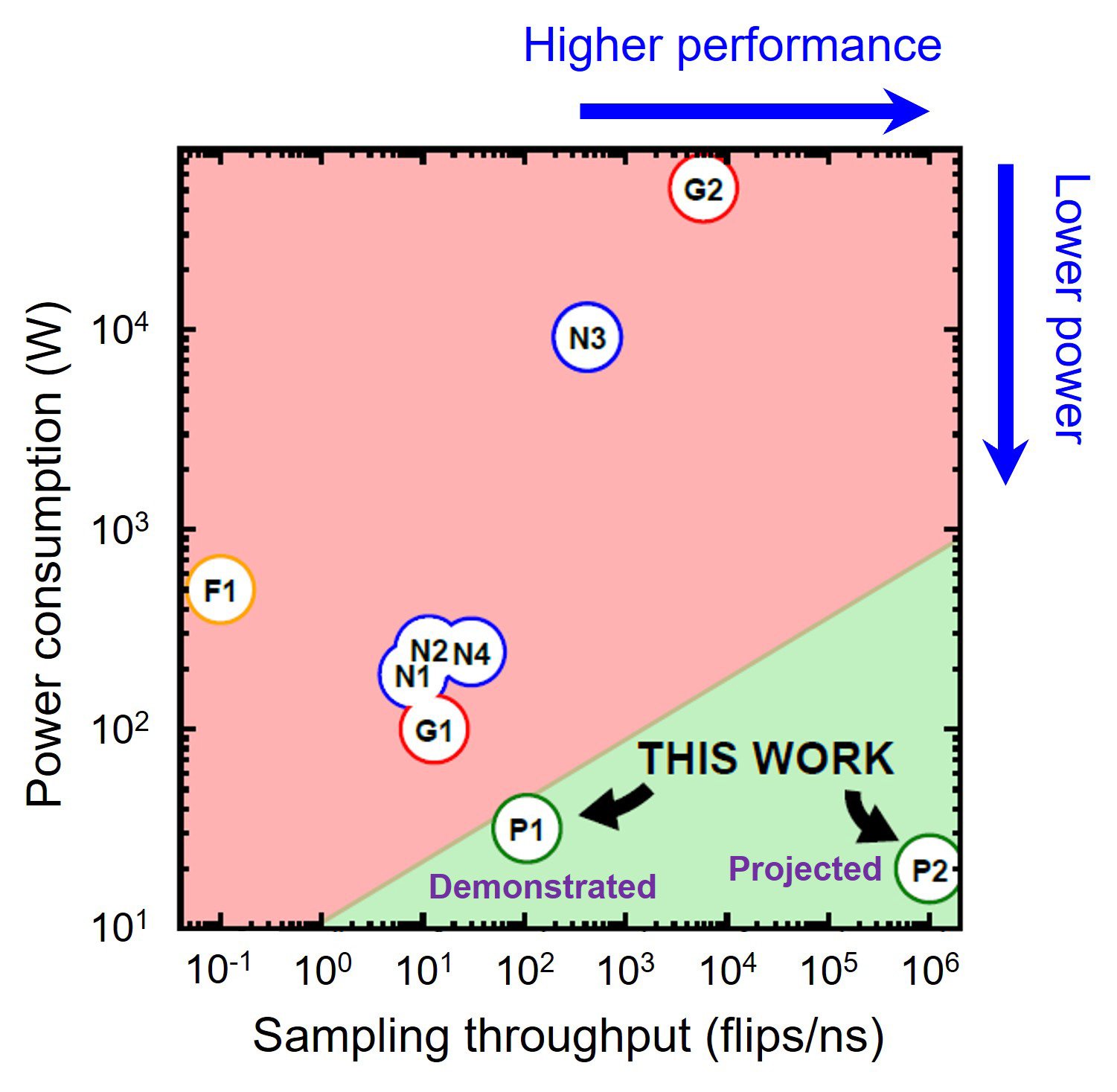

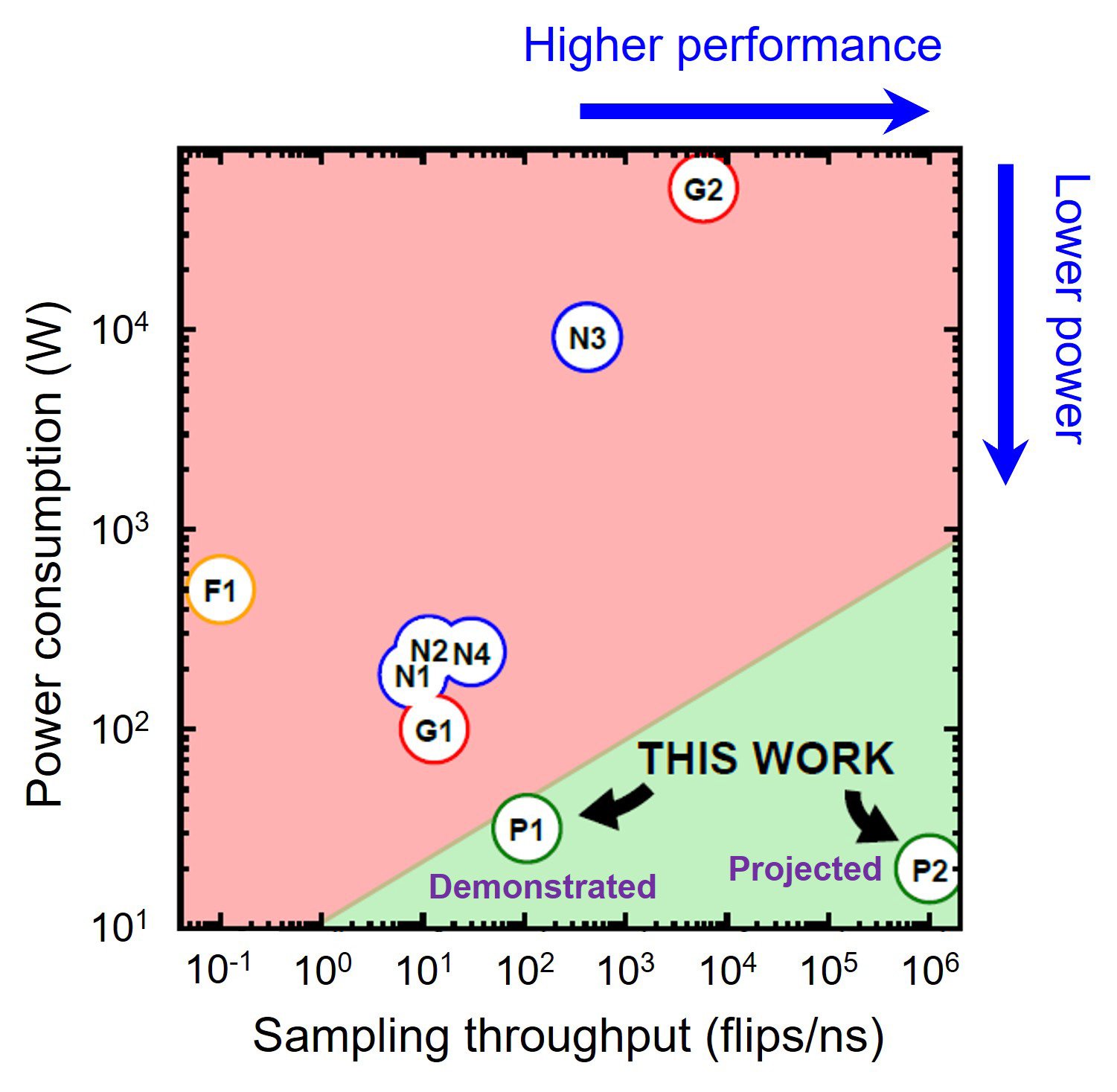

| A comparability of probabilistic accelerators as a perform of sampling throughput and energy consumption. Graphics Processing Items (GPUs) [plotted as N1-N4], Tensor Processing Items (TPUs) [plotted as G1-G2], and simulated annealing machine [plotted as F1] are in contrast with probabilistic computer systems, the place demonstrated worth and projected worth are plotted as P1 and P2, respectively. (Picture: Kerem Camsari, Giovanni Finocchio, and Shunsuke Fukami et al.)

|

|

The researchers additionally benchmarked the efficiency of sMTJ-based p-computers with that of classical computing {hardware}, akin to graphics processing models (GPUs) and Tensor Processing Items (TPUs). They confirmed that p-computers, using a high-performance sMTJ beforehand demonstrated by a group from Tohoku College, can obtain huge enhancements in throughput and energy consumption than typical applied sciences.

|

|

“Presently, the “s-MTJ + FPGA” p-computer is a prototype with discrete parts,” mentioned Professor Shunsuke Fukami, who was a part of the analysis group. “Sooner or later, built-in p-computers that make use of semiconductor process-compatible magnetoresistive random entry reminiscence (MRAM) applied sciences could also be attainable, however this can require a co-design strategy, with specialists in supplies, physics, circuit design and algorithms needing to be introduced in.”

|